RAM nội

Trong các FPGA sau này đều có các khối RAM tĩnh được điều khiển bởi các thành phần lô-gic

Block RAM - khối RAM trong FPGA

Xử lý của RAM nội

Có rất nhiều thông số tác động lên xử lý của RAM nội. Thông số chính là “số tác nhân” có thể truy cập RAM cùng một lúc.

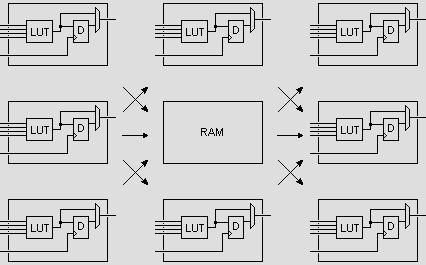

- “single-port” RAM (RAM đơn port): chỉ một tác nhân có thể đọc/ghi RAM

- “dual-port” RAM (RAM 2 port), “quad-port” RAM (RAM 4 port): Có hai/bốn tác nhân có thể đọc/ghi RAM. Mỗi tác nhân có thể sử dụng clock khác nhau, điều này rất quan trọng khi ta cần chuyển dữ liệu từ miền clock này sang miền clock kia.

Để tính xem có bao nhiêu tác nhân có thể truy cập

RAM thì ta đếm số bus địa chỉ. Mỗi tác nhân có một bus địa chỉ riêng,

một bus đọc dữ liệu và một bus ghi dữ liệu.

RAM 2 port (2 tác nhân truy cập)

Việc ghi vào RAM luôn luôn được thực hiện đồng bộ. Việc đọc cũng vậy nhưng có đôi khi được thực hiện bất đồng bộ.

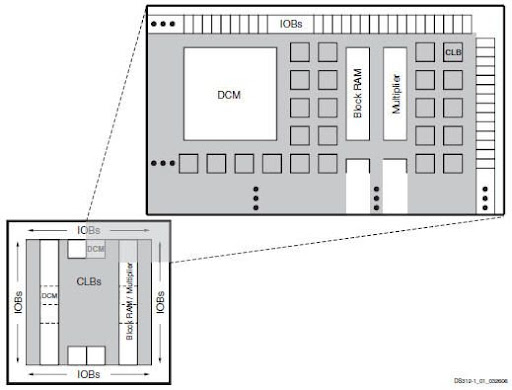

RAM khối (Blockram) và RAM phân bố (Distributed RAM)

Hiện tại có hai loại RAM nội trong FPGA là RAM khối và RAM phân bố. Kích thước RAM dùng để xác định loại được sử dụng.

Các khối RAM lớn gọi là “RAM khối”, nó được đặt

trong các vùng chuyên biệt trong RAM. Mỗi FPGA có một số giới hạn loại

RAM này và chúng chỉ có chức năng là RAM chứ không thể dùng cho bất cứ

chức năng nào khác.

Các

khối RAM nhỏ đặt trong các “RAM khối nhỏ hơn” (Altera) hoặc dưới dạng

“RAM phân bố” (Xilinx). “RAM phân bố” cho phép dùng các logic-cell của

FPGA như là các RAM cực nhỏ, loại RAM này phân bố linh động trong FPGA

mà không gom chung trong một vùng (một logic-cell giống như một RAM cực

nhỏ). Altera thì xây dựng các “RAM khối” với kích thước khác nhau đặt

khắp trong lịn kiện nhưng độ linh động vẫn không bằng “RAM phân bố”.

0 comments:

Post a Comment