FPGA có cấu tạo như thế nào

Cấu tạo cơ bản của FPGA

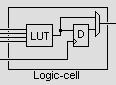

Các logic-cell

FPGA có cấu tạo từ các logic-cell. Về cơ bản một

logic-cell gồm một bảng tra (LUT), một Flip-Flop và một mux 2 sang 1 (để

có thể bỏ qua Flip-Flop nếu muốn). Một LUT giống như một RAM nhỏ có thể

thực thi một chức năng lô-gic nào đó và LUT có các ngõ vào (input). Ví

dụ như hình minh họa là 4 ngõ vào.

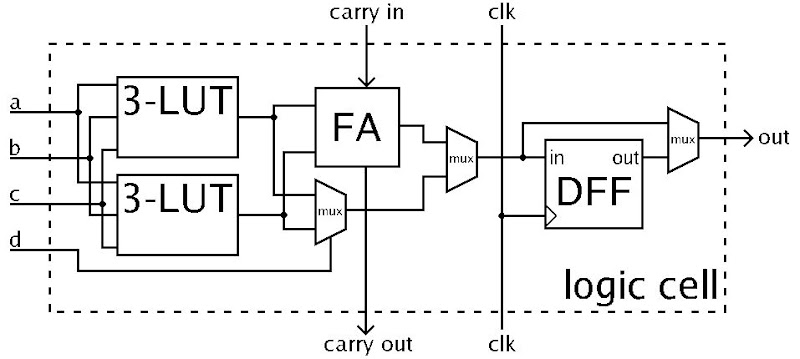

Ví dụ về logic-cell

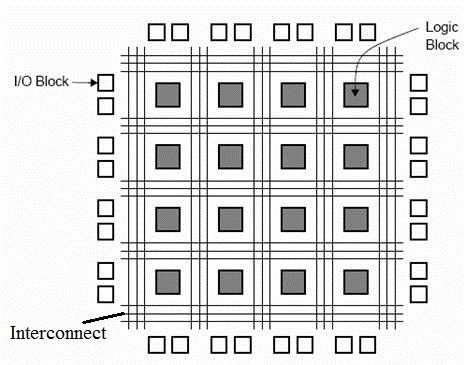

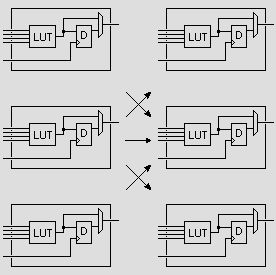

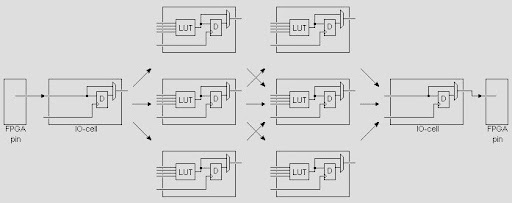

Kết nối logic-cell (Interconnect)

Các logic-cell được kết nối với nhau thông qua các

“tài nguyên liên kết”, là các dây nối và mux được đặt xung quanh

logic-cell. Mỗi logic-cell có thể nhỏ nhưng có rất nhiều các kết nối đến

chúng để có thể tạo ra các chức năng lô-gic phức tạp.

Các IO-cell

Các dây nối còn được đưa đến biên của linh kiện. Biên linh kiện có đặt các IO-cell để kết nối ra các chân của FPGA.

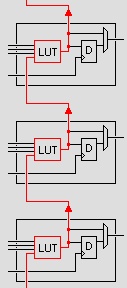

Các chuỗi nhớ và định tuyến chuyên dụng (Dedicated routing/carry chains)

Bên cạnh các kết nối thông thường thì các “tài

nguyên kết nối đa năng” cũng được thêm vào. Trong FPGA, các logic-cell

liền kề nhau có các đường kết nối nhanh chuyên dụng (fast dedicated

lines). Loại đường nhanh chuyên dụng phổ biến nhất là “chuỗi nhớ” (carry

chains). Chuỗi nhớ cho phép tạo các chức năng toán học (như bộ đếm và

bộ cộng) rất hiệu quả với tài nguyên logic thấp và tốc độ xử lý cao.

Với các công nghệ thấp hơn như PAL hay CPLD thì

không có các “chuỗi nhớ” này vì vậy tốc độ bị giới hạn khi các xử lý

toán học được yêu cầu.

0 comments:

Post a Comment